高速高周波対応基板・超高密度対応基板設計技術を活用した開発事例をご紹介します。

お客様

某製造業 様

業種

画像認識機器に関する開発・設計および試験・検査

■お困りごと

当社の提供技術:基板回路設計、熱解析・熱設計、SI/PI解析、電源共振解析

基板レイアウト構想において、信号/電源品質水準を満たす形で指定基板サイズ内に部品を配置することが求められました。既存の筐体を流用することから、基板サイズを変更せずに要求性能を実現するため、以下の提案をしました。

1.適切な基板層構成の提案(基板回路設計)

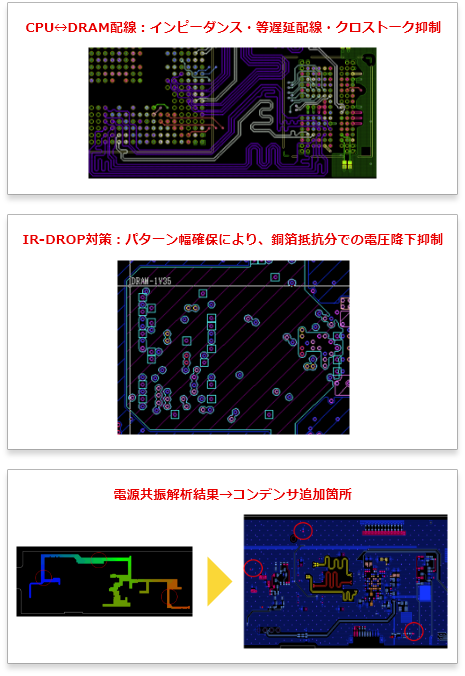

各電源の電流容量や低電圧電源IR-DORPにおいて基準を満たす電源パターン形成とリターンGND確保。DRAMメモリのBytelane毎の等遅延配線とインピーダンスコントロールを実施し、信号/電源品質を確保する基板層構成を提案。

2.SIシミュレーションのポスト解析(シミュレーション・解析)

各層毎の伝搬遅延、VIA損失を考慮した、CPU/DRAMの適切な配線を実施。各種シミュレーション・解析を行い、問題無い事を確認。また、信号間クリアランスを十分に確保し、クロストークを抑制。信号パターンのインピーダンス安定化を実現。

3.PI(電源品質)確保とEMI予防策(電源共振解析~要因特定)

電源/リターンGNDのパターン幅・VIAを確保することにより、IR-DROPでCPU動作電圧以下とならないよう設計した。また、各電圧電源に対し電源共振解析を実施し、EMIの要因となりそうな箇所にコンデンサを追加する対策を実施、電源品質を担保。

基板サイズの制限がある中で電源品質を担保し、障害の要因となるであろう箇所を特定し、予防策を実施しました。

お客様要望を整理し、綿密な進捗確認と最適化調整の結果、

既存基板サイズを変えることなく各要求水準を満たすイメージセンサユニットを実現しました。

■設計物の概要