CAE

培った電気シミュレーション技術と高速回路シミュレーション技術で、

ノイズに強い高速デジタル回路の設計やノイズ対策部品の削減を提案。

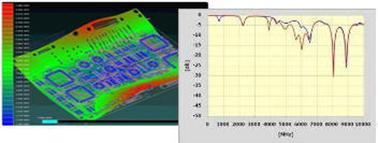

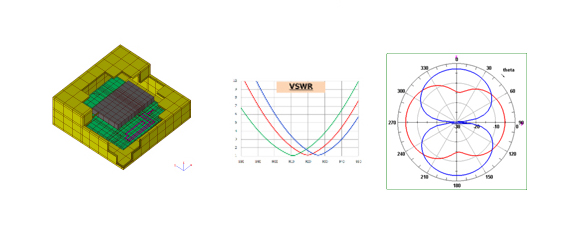

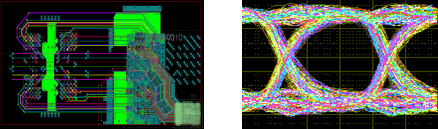

高速デジタル回路基板の設計プロセスで大きな時間のロスを招く要因の一つが、実機評価段階で問題が発覚し、設計の後戻りが発生することです。このロスが製品化を遅らせ、発売時期を遅らせる致命傷にもなりかねません。そこで、基板レイアウト設計の上流段階で電気のシミュレーション技術を駆使し、ノイズなどの問題がまったくないことを確認してから、次のプロセスへ進むことが、品質のよい設計を実現します。 上流設計段階で行う電気シミュレーションは、高速信号の波形品質の解析、基板上に形成するアンテナ特性解析、電源ノイズ対策部品やEMI対策部品の個数削減(部品コスト低減)や配置の最適化を行うための電磁界解析など。新規チップセットを採用した開発を行うときは、超高速回路シミュレーション技術を駆使し、基板レイアウト設計者向けの配線ガイドを構築することもあります。また、これまでのシミュレーションと実測との比較結果を新規シミュレーションのモデリングに反映することで、常に精度を向上。こうした実績の積み重ねにより、新規の回路設計でも後戻りのない、高性能な製品開発を実現します。

※CAE(Computer Aided Engineering)